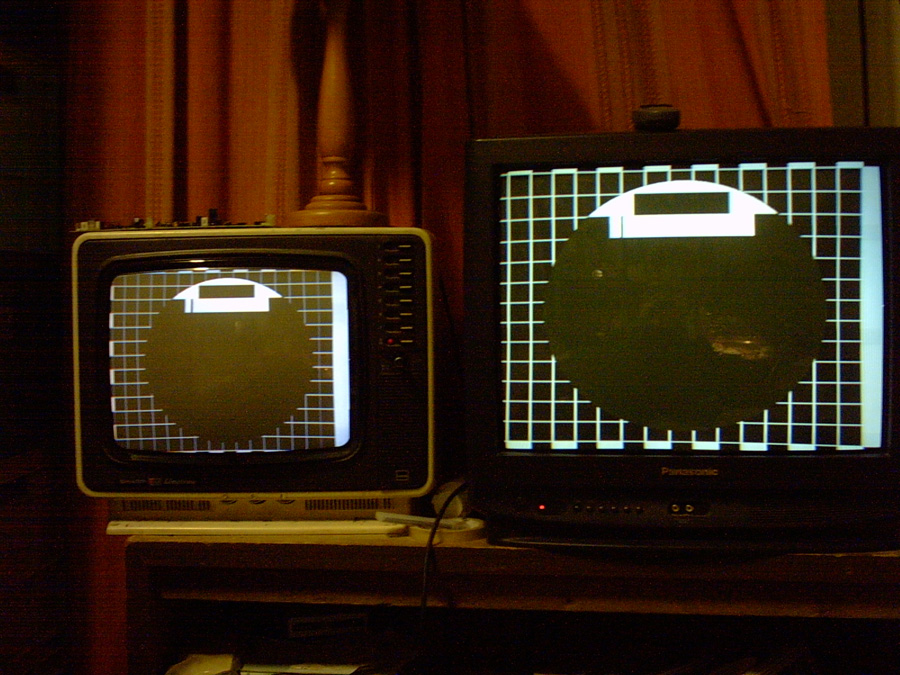

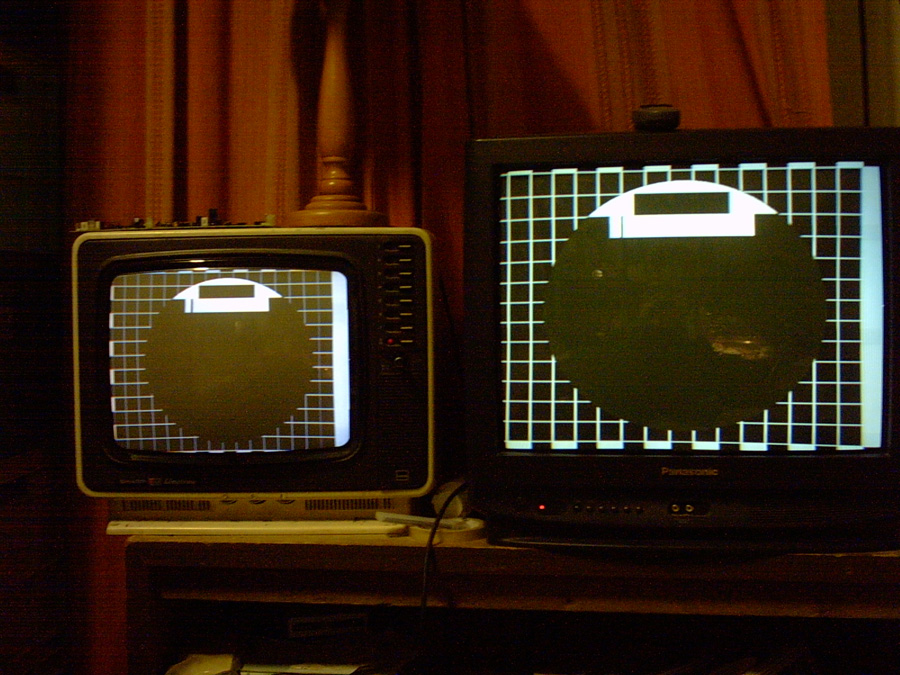

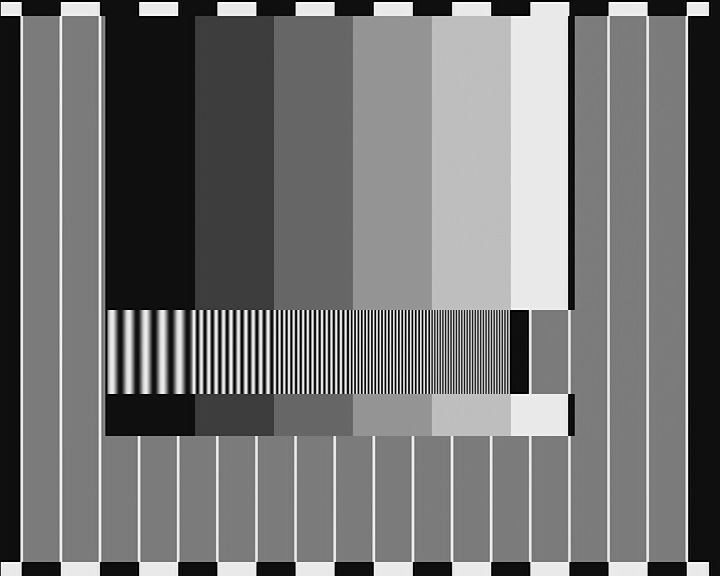

Early stages - B&W only

** NEW PM5544 PROJECT FOR 2012! SCROLL DOWN! **

|

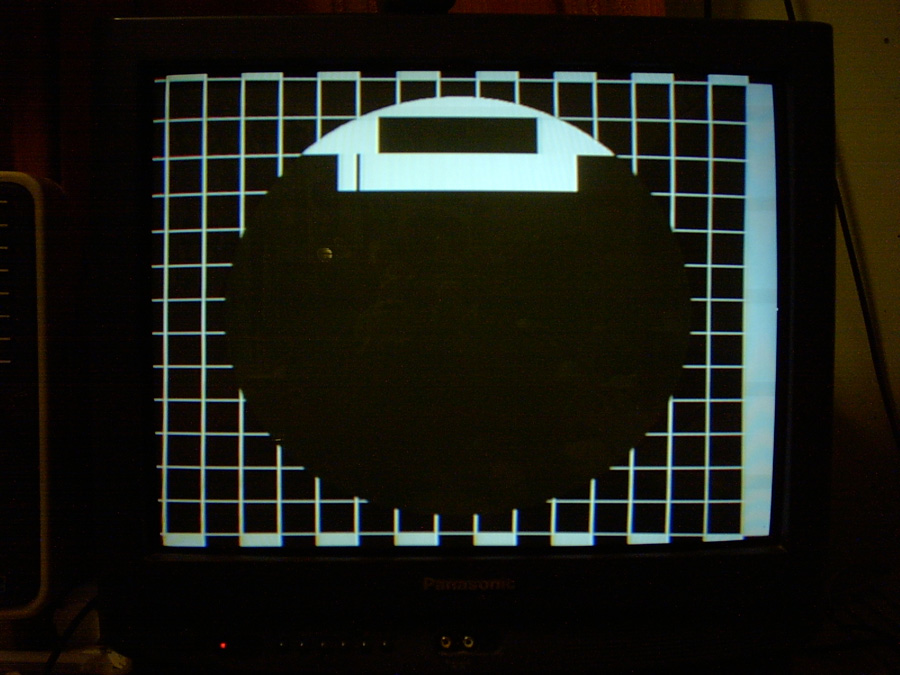

| The picture is composed of blocks of image

data (kinda like video LEGO!)

Getting the circle to work was a milestone, as it required very close timing that wasn't possible in software using this approach. It was finally accomplished by using the hardware timer to switch foreground/background colours, using a RAMDAC chip programmed with the colours grouped into layers. The RAMDAC was an old TR9C1710 scavenged from a VGA card. It converts the 1-byte colour codes to 6-bit RGB values and does D to A conversion. This saved I/O pins on the microcontroller and

made the software faster.

|

|

|

Every visible part of the PM5543 was able to be coded easily EXCEPT the frequency gratings. The samplerate using a 16MHz processor was far too low for software DDS. Even hard-coding the gratings at 2 instructions per sample was too slow for the 4.8MHz grating. This equates to 8MHz sampling, resulting in a maximum frequency of 4MHz. Preloading lots of registers (the MEGA-8 has 32) with greyscale data and outputting one sample per clock period may have made it possible, as it would achieve a 16MHz video sample rate (8MHz bandwidth). This would require the software to be rewritten to use RAM storage for most variables. A modern 40MHz+ DSP controller with DMA and

more RAM should have no trouble generating all the PM5543 components, though

the software would need to be completely different.

|

|

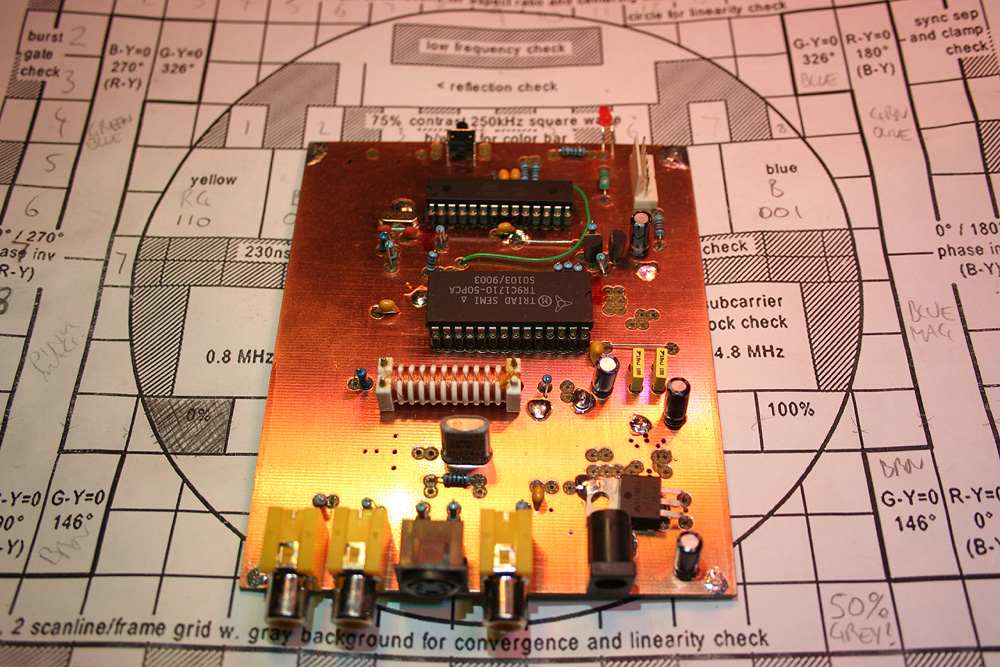

| The new homebrew "Philips PM5544 test pattern generator" PCB. It features an Atmel Mega88 microcontroller, a VGA RAMDAC, and an SMD MC13077 PAL colour encoder chip. Each chip cost under $10 AU. The RAMDAC was removed from an old VGA card, so it was free! |

|

| The colour encoder chip is on order at this stage, so the video output is temporarily wired as monochrome only. The funny looking white thing to the left of the RAMDAC is a video luminance delay line, to compensate for the delay in processing the colour signal. The colour encoder IC is a surface mount chip that is mounted on the PCB underside. |

|

Greyscale & Sinewave TestUsing an Atmel Mega88 microcontroller @20MHz, it was possible to generate sinewaves at 20MSPS by preloading a group of 20 registers with greyscale data - to do output in a single clock cycle each. This required efficient usage of the Mega88's 32 working registers. No RAM variables were needed after all! |

|

|

| Nov 14, 2012

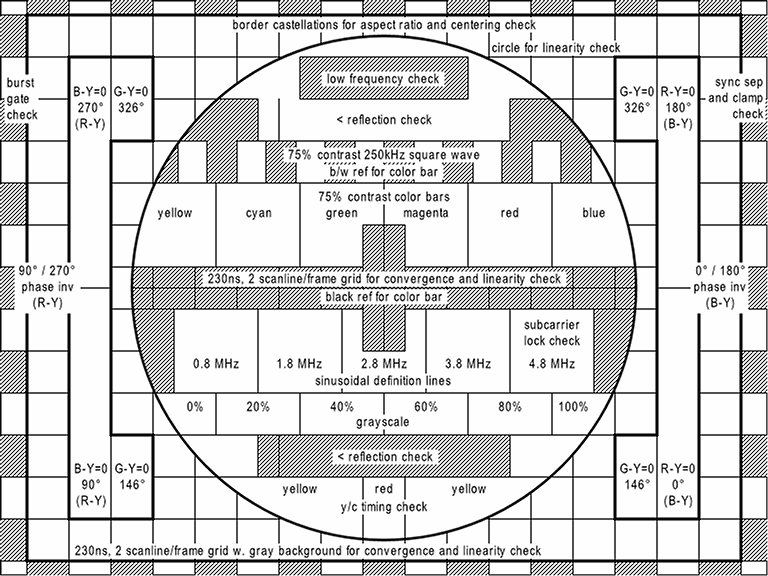

From Wikipedia (public domain images) Here is a reference "Philips PM5544 test pattern" and a reference chart, showing the various components of the pattern. The following differences from the AVR pattern generator are noted:

Some specs from the AVR design (after recent efficiency improvements):

|

|

A DSP approach

Advantages of this approach include:

The next step will be to try to output some test signals read from a memory buffer, to check signal timing and quality. Using an 8-bit DAC should enable TRUE COLOUR output (256 levels per channel) but only in composite mode. In s-video mode only 4 bits would be available (16 levels) with an 8-bit port - not very practical. The AVR board above uses a timed approach to video generation. It outputs a YUV colour value then waits for the next one. This means the CPU spends a lot of it's time doing nothing, enabling it to do other background functions. A DSP approach is more work, because the CPU has to output every pixel individually. Although where lines have the same data, it can do nothing and just let the DMA read out the same line again! Also, where a line is different the CPU can just update the changed parts and leave the rest of the line alone. These shortcuts might reduce the CPU workload enough to make test pattern generation practical. The dsPIC33FJ64GP802 flash memory (64k) and RAM (16k) are both large enough that the entire image might be able to be coded in RLE (Run Length compression) and stored on-chip. This would reduce the need for on-the-fly computations. It would also enable any kind of pattern to be produced.

|

|

DSP Video TestAn early version of the software is generating composite sync with a black and white checkerboard pattern. Testing has shown the dsPIC33FJ64GP802 parallel port to be too slow for 4x chroma sampling, but well suited for 3x chroma sampling (13.3MHz). A single chip version of the pattern generator isn't possible, because an 8-bit latch is required for stable output, as the PMP data output is always multiplexed (even with no multiplexed functions selected). However, the extra chip required (74HC574) is cheap, and readily available.

|

|

|

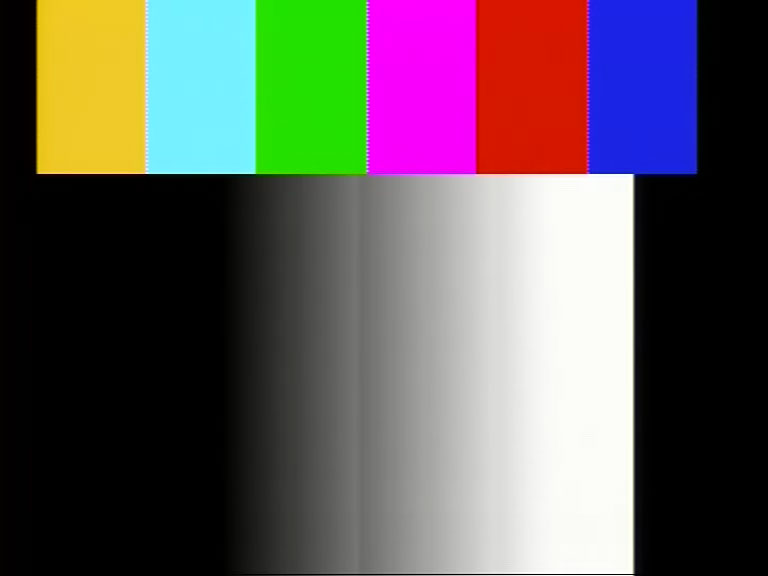

DSP Colour Bars and RampThe breadboard version of the DSP pattern generator is now functional, producing colour bars and a ramp. Problems:

The chroma phasing has a problem, in that the picture line count has to be EVEN or the colour fails to work. This is due to a timing issue. Since the sampling is chroma locked, the total number of chroma samples has to be correct for both the phase and frequency to be correct. Solid colour areas have good quality. Colour edges are very sharp - with perfect Y/C alignment, but have some fixed patterning - either due to the line & chroma frequencies being locked together, or the interaction of the sample data as it crosses over from one sample group to the next. Either the sync position or the chroma phase needs to continuously rotate to offset the frequencies and make the patterning move. DSP filtering may be needed to process the sample values as they change from one block to the next. Processing is difficult, as there are 3 (byte) samples in each group (24 bits), yet the dsPIC chip processes data in 16 bit format (2 samples at a time). The R-2R DAC is showing some glitches in the ramp waveform. This is probably due to the imprecise resistor ratio (1k & 2k2), output impedance effects of the CMOS gate, or poor grounding due to the circuit being built on a plugin breadboard. Also there is currently no anti-alias lowpass filter on the video output, apart from one 33pF capacitor.

|

ImprovementsNew experiments using 16 bit DMA and PMP transfer modes have shown that it is possible to operate the DMA driven data port at 4 times the chroma frequency (17.734475 MHz). This is very advantageous, as it makes the chroma and luma timing work together. The 4x chroma sample rate is a very close multiple of line frequency (1135.0064 times). This results in the frequencies and phases being correct automatically, with a tiny error of only 0.64% (100Hz at 15.625kHz). This may still be significant for critical applications. It also means 4 byte groups represent each colour sample, which fits in better with the 16 bit buffer transfers than the 3 byte groups when operating at 3x chroma frequency. In 16 bit mode the PMP needs double latching to make the DAC work correctly. This means using a minimum of 2 ICs to build the video DAC instead of 1. It also requires faster data latches than currently used. Using a proper video DAC, one high speed latch and a fast flip-flop to provide a pixel clock from the CPU clock should work. Unfortunately the readily available video DAC has the data pin ordering in reverse to the dsPIC PMP port. One way to correct this is to mount the DAC flipped upside-down, after reforming the leads. Another way is to use an SMD version of the dsPIC mounted in a SMD adaptor board. This also enables the SMD chip to be unplugged. Using 4x chroma sampling means the CPU will be running 2x this speed (35.46895 MHz), unless another workable timing ratio can be found **. This gives the CPU only a 2:1 raw speed advantage over the DMA, though the 16 bit buffer transfers provide another 2x speedup. This hopefully means that the CPU has a 4x faster ability to write to the buffer than the DMA reads it. The dsPIC hardware repeat and do loops also help to speed the process of writing video to the buffer. **The dsPIC33E could run at 70.9379 MHz (slightly overclocked), and possibly other intermediate speeds, using various PMP wait states. The structure of the new pattern generator software will be a little different, because the DMA buffer is too small to store 2 lines of video at 17.73 MHz, unless the buffer is only used for about 57.7 uS of the 64 uS line. This is one reason why the CPU must run at a precise multiple of the DMA rate, so a hardware timer can generate the sync pulses with exact timing, then return to DMA mode for the visible portion of the line. Using this technique allows alternate lines to be saved in each 1k buffer. This works well with the PAL phasing, and allows video lines that don't change to be read out a second time with no CPU effort. The dsPIC33E with a 4k DMA buffer would avoid this 1k buffer limitation, and double the CPU speed at the same time.

|

Better Hardware Alternatives?dsPIC33E series

Philips SAA7120

ST Micro STi5518

The benefits:

The problems:

|